## MATTHIEU LOUMAIGNE

# ÉLECTRONIQUE NUMÉRIQUE

M1 PHYSIQUE - UNIVERSITÉ D'ANGERS - JANVIER 2022

## Table des matières

| I   |              |                                                | 7  |

|-----|--------------|------------------------------------------------|----|

| 1   | Logique Bo   | ooléenne                                       | 9  |

| 1.1 | Quelques     | définitions                                    | 9  |

|     | 1.1.1        | Variable binaire                               | 9  |

|     | 1.1.2        | Fonction binaire                               | 9  |

|     | 1.1.3        | Table de vérité                                | 9  |

| 1.2 | Expression   | ns booléennes                                  | 9  |

| 1.3 | Représenta   | ation canonique                                | 10 |

| 1.4 | Deux théo    | rèmes de l'algèbre booléenne                   | 11 |

|     | 1.4.1        | Les théorèmes de Boole                         | 11 |

|     | 1.4.2        | Les théorèmes de De Morgan                     | 11 |

| 1.5 | Les portes   | logiques                                       | 12 |

|     | 1.5.1        | Porte NON (NOT)                                | 12 |

|     | 1.5.2        | Porte OU (OR)                                  | 12 |

|     | 1.5.3        | Porte ET (AND)                                 | 12 |

|     | 1.5.4        | Porte OU-EXCLUSIF (XOR)                        | 12 |

|     | 1.5.5        | Porte NON-ET (NAND)                            | 12 |

|     | 1.5.6        | Porte NI (NOR)                                 | 13 |

|     | 1.5.7        | Multiplexeur (MUX)                             | 13 |

|     | 1.5.8        | Demultiplexeur (DMUX)                          | 13 |

| 1.6 | Mise en pi   | ratique                                        | 14 |

| 1.7 | TP / TD.     |                                                | 14 |

|     | 1.7.1        | Quelques exercices autour de l'algébre boléene | 14 |

|     | 1.7.2        | De l'universalité de la porte NAND             | 15 |

| 2   | Arithmétiq   | ue Booléenne                                   | 17 |

| 2.1 | Les nombi    | res binaires                                   | 17 |

| 2.2 | Addition b   | oinaire                                        | 17 |

| 2.3 | Nombre b     | inaire algébrique                              | 18 |

| 2.4 | Représenta   | ation d'un nombre en virgule fixe              | 19 |

|     | 2.4.1        | La réprésentation en virgule flotante          | 19 |

|     | 2.4.2        | La réprésentation en virgule fixe              | 19 |

|     | 2.4.3        | La multiplication                              | 21 |

|     | 2.4.4        | La division par 2                              | 21 |

| 2.5 | Les addition | onneurs                                        | 21 |

|     | 2.5.1        | Le demi additionneur                           | 22 |

|     | 2 - 2        | L'additionnour complet                         | 22 |

| 2.5.3          | L'additionneur                               | 22 |

|----------------|----------------------------------------------|----|

| 2.5.4          | Incrémenteur                                 | 24 |

| 2.6 L'unité A  | rithmétique et Logique (ALU)                 | 24 |

| 2.7 TD 2       |                                              | 26 |

| 2.7.1          | Complément à 2                               | 26 |

| 2.7.2          | Additionneur                                 | 27 |

| 2.7.3          | ALU                                          | 27 |

| 3 Logique sé   | equentielle                                  | 29 |

| 3.1 Quelques   | généralités                                  | 29 |

| 3.1.1          | Horloge                                      | 29 |

| 3.1.2          | Bascules                                     | 30 |

| 3.1.3          | Compteurs                                    | 30 |

| 3.2 Implémer   | ntation Bascules à partir de portes logiques | 30 |

| 3.2.1          | Boucler des portes logiques                  | 30 |

| 3.2.2          | Bascule RS                                   | 31 |

| 3.2.3          | Bascule D                                    | 31 |

| 3.3 Implémer   | ntation de la mémoire à partir de bascule    | 32 |

| 3.3.1          | Registre                                     | 32 |

| 3.3.2          | Random Access Memory                         | 33 |

| 3.3.3          | Compteur                                     | 33 |

| 3.4 TD 3       |                                              | 33 |

| 3.4.1          | bascule D                                    | 33 |

| 3.4.2          | Registre                                     | 33 |

| 3.4.3          | RAM                                          | 35 |

| 3.4.4          | Compteur                                     | 35 |

| 4 Langage m    | aachine                                      | 37 |

| 4.1 Architectu | ure de l'ordinateur                          |    |

| 4.1.1          |                                              |    |

| 4.1.2          | Central Processing Unit (CPU)                | 38 |

| 4.1.3          | Notre architecture                           | 39 |

| 4.2 Langage r  | machine                                      | 41 |

| 4.2.1          | Notre ordinateur                             | 41 |

| 4.2.2          | Instruction adresse                          | 42 |

| 4.2.3          | Instruction calcul                           | 42 |

| 4.2.4          | Instruction vidéo                            | 44 |

| 4.3 Programn   | nation                                       | 45 |

| 4.3.1          | Addition de deux nombres                     | 45 |

| 4.3.2          | Multiplication                               | 48 |

| 4.4 TD 4       |                                              | 51 |

| 4.4.1          | Réalisation du circuit de condition de jump  | 51 |

| 4.4.2          | Le programme counter                         | 52 |

| 4.4.3          | CPU                                          | 52 |

| 4.4.4          | L'ordinateur                                 | 53 |

| 4.4.5          | Factorielle                                  | 53 |

| 11   | M1cro-co    | ntroleur                                       | 57 |

|------|-------------|------------------------------------------------|----|

| 5    | Quelques g  | généralités sur les microcontroleurs           | 59 |

| 5.1  | Arduino .   |                                                | 60 |

|      | 5.1.1       | Présentation de la plateforme                  | 60 |

|      | 5.1.2       | Getting started                                | 60 |

| 5.2  | Interuptio  | on                                             | 61 |

| 6    | TP cours s  | ur la plateforme Arduino                       | 63 |

| 6.1  | Sortie nur  | nérique                                        | 63 |

|      | 6.1.1       | Lire la doc (RTFM)                             | 63 |

|      | 6.1.2       | Faire clignoter la LED placée sur la carte ar- |    |

|      |             | duino (pin 13)                                 | 63 |

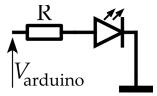

|      | 6.1.3       | Faire clignoter une LED externe                | 64 |

|      | 6.1.4       | Emettre SOS en Morse                           | 64 |

|      | 6.1.5       | Jouer une mélodie                              | 64 |

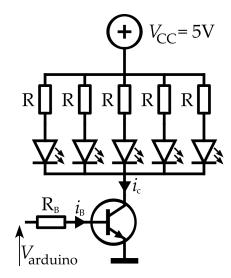

|      | 6.1.6       | Piloter un interrupteur avec l'arduino         | 65 |

| 6.2  | Communi     | ication par la voie série                      | 65 |

|      | 6.2.1       | Lire la doc (RTFM)                             | 66 |

|      | 6.2.2       | Communication de l'arduino vers l'ordinateur . | 66 |

|      | 6.2.3       | Communication de l'ordinateur vers l'arduino . | 66 |

| 6.3  | Sorties PV  | VM                                             | 67 |

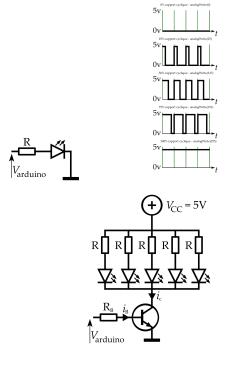

|      | 6.3.1       | Lire la doc (RTFM)                             | 67 |

|      | 6.3.2       | Etude du signal à l'oscilloscope               | 67 |

|      | 6.3.3       | Modulation de l'intensité d'une LED            | 68 |

| 6.4  | Entrée nu   | mérique - digital read                         | 68 |

|      | 6.4.1       | Lire la doc (RTFM)                             | 68 |

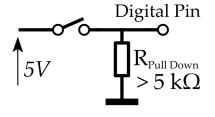

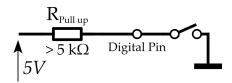

|      | 6.4.2       | Les résistances de pull-up                     | 69 |

| 6.5  | ADC Ana     | log to Digital Conversion                      | 71 |

|      | 6.5.1       | Lire la doc (RTFM)                             | 71 |

|      | 6.5.2       | Utilisation d'un potentiomètre                 | 71 |

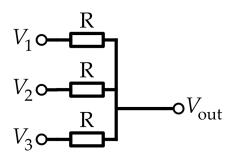

| 6.6  | DAC Digi    | tal to Analog Conversion                       | 71 |

|      | 6.6.1       | PWM                                            | 71 |

| 6.7  | Interuptio  | n                                              | 71 |

| 6.8  | Timer       |                                                | 71 |

| 6.9  | Utiliser de | es commandes plus bas niveau                   | 71 |

| 6.10 | Mini Proje  | et                                             | 71 |

| Bib  | liographie  |                                                | 73 |

| A    | Quelques (  | éléments de corrections des TD                 | 75 |

## 1 Logique Booléenne

## 1.1 Quelques définitions

#### 1.1.1 Variable binaire

L'algèbre booléenne manie des grandeurs binaires <sup>1</sup> dite booléennes et qui sont typiquement appelées vrai/faux, 1/0, oui/non, on/off, etc...

#### 1.1.2 Fonction binaire

Une fonction booléenne est une fonction qui opère avec des grandeurs booléens en entrée et retourne des valeurs booléennes.

#### 1.1.3 Table de vérité

Une table de vérité énumère toutes les cas possibles d'une fonction booléenne. Plus précisément, la table de vérité répertorie de façon exhaustive toute les combinaisons possibles de valeurs d'entrée et en donne les valeurs de sortie correspondantes (voir par exemple la table 1.1).

x

y

z

f(x,y,z)

0

0

0

0

0

1

0

1

0

0

1

1

0

1

1

1

0

0

1

1

0

1

1

0

1

1

1

## Table 1.1: Un exemple de table de vérité pour la fonction booléenne fx, y, z)

## 1.2 Expressions booléennes

Une fonction booléenne peut aussi être décrite en appliquant des opérations booléennes sur les variable d'entrées. Listons les trois principales opérations :

1. On travaille avec des valeurs binaires (o et 1) et non décimale avant tout pour des raisons technologiques, il est beaucoup plus facile de creer un interrupteur avec l'état ouvert ou fermé qu'un système permettant de contrôler et de mesurer de manière robuste

des valeurs intermédiaires.

| Fonction                   | x                                             | 0 | 0 | 1 | 1 |

|----------------------------|-----------------------------------------------|---|---|---|---|

| Poliction                  | y                                             | 0 | 1 | 0 | 1 |

| Constante o                | 0                                             | О | О | O | 0 |

| And                        | $x \cdot y$                                   | О | o | O | 1 |

| x And Not y                | $x \cdot \overline{y}$                        | О | o | 1 | О |

| x                          | x                                             | О | o | 1 | 1 |

| Not x And y                | $\overline{x} \cdot y$                        | О | 1 | O | О |

| y                          | y                                             | О | 1 | O | 1 |

| Xor                        | $x \cdot \overline{y} + \overline{x} \cdot y$ | О | 1 | 1 | О |

| Or                         | x + y                                         | О | 1 | 1 | 1 |

| Nor                        | $\overline{x+y}$                              | 1 | O | O | О |

| Equivalence                | $x \cdot y + \overline{x} \cdot \overline{y}$ | 1 | O | O | 1 |

| Not y                      | $\mid \overline{y} \mid$                      | 1 | o | 1 | О |

| Si <i>y</i> alors <i>x</i> | $x + \overline{y}$                            | 1 | o | 1 | 1 |

| Not x                      | $\overline{x}$                                | 1 | 1 | O | О |

| Si <i>x</i> alors <i>y</i> | $\overline{x} \cdot y$                        | 1 | 1 | o | 1 |

| Nand                       | $\overline{x \cdot y}$                        | 1 | 1 | 1 | О |

| Constant 1                 | 1                                             | 1 | 1 | 1 | 1 |

Table 1.2: Liste de toutes les fonctions booléennes de 2 variables. Il en existe  $2^4 = 16$ .

"And" (et) "x And y" vaut 1 exactement quand x et y valent 1. Cette opération est notée :

$$x$$

and  $y \equiv x \cdot y$

"Or" (ou) "x Or y" vaut exactement 1 quand x ou y vaut 1. Cette opération est notée :

$$x \text{ or } y \equiv x + y$$

"Not" (non) "Not x" vaut exactement 1 quand x vaut o. Cette opération se note:

Not

$$x \equiv \overline{x}$$

La liste de toutes les fonctions booléennes possibles est donnée dans le tableau 1.2.

## Représentation canonique

N'importe quelle fonction booléenne, aussi compliquée soit-elle peut s'exprimer en n'utilisant que trois opérateurs booléens : et, ou et non.

De plus, a minima, toute fonction booléenne peut toujours être écrite sous au moins une forme qui est appelée la représentation canonique.

On peut facilement obtenir cette représentation canonique en partant de la table de vérité (voir par exemple la table 1.1 pour fixer les idées). La méthode systématique est alors la suivante :

1. On ne regarde que les lignes de la table de vérité où la fonction booléenne (ici f(x, y, z)) vaut 1.

2. Pour chacune de ces lignes, on construit un terme en utilisant uniquement l'opérateur et (·). Plus précisément, on applique l'opérateur et en utilisant x lorsque x égale 1 et en utilisant  $\overline{x}$  lorsque x égale 0.

Par exemple pour la troisième ligne, nous obtenons le terme  $x\cdot \overline{y}\cdot z$ .

3. Nous appliquons l'opérateur ou (+) à chacun de ces termes.

Dans le cas de la table 1.1 nous obtenons donc :

$$f(x, y, z) = x \cdot \overline{y} \cdot z + \overline{x} \cdot y \cdot z + \overline{x} \cdot \overline{y} \cdot z$$

Ainsi, il existe toujours une façon d'exprimer une fonction booléenne avec seulement les trois opérateurs booléens : *et*, *ou* et *non*. Ce n'est évidemment généralement pas la seule expression possible <sup>2</sup> et, généralement, la représentation canonique n'est pas la représentation la plus compacte d'une fonction booléenne. Ces écriture plus compact peuvent par exemple être obtenues via les théorèmes de Boole et de De Morgan.

2. En terme plus mathématiques, il n'y a *pas unicité* de la représentation algébrique d'une fonction booléenne

## 1.4 Deux théorèmes de l'algèbre booléenne

#### 1.4.1 Les théorèmes de Boole

Les théorèmes de Boole sont donnés dans le tableau 1.3. Pour la plupart, il s'agit presque d'évidence.

| Complémentarité           | $a + \overline{a} = 1$ , $a \cdot \overline{a} = 0$ , $\overline{\overline{a}} = a$ |

|---------------------------|-------------------------------------------------------------------------------------|

| Idempotence               | $a+a+a+\ldots=a$ , $a\cdot a\cdot a\cdot \ldots=a$                                  |

| Éléments neutres          | $a+0=a  ,  a\cdot 1=a$                                                              |

| Éléments absorbants       | $a+1=1  ,  a\cdot 0=0$                                                              |

| Commutativité             | $a+b=b+a$ , $a \cdot b=b \cdot a$                                                   |

| Associativité             | (a+b) + c = a + (b+c) = a+b+                                                        |

|                           | $c$ , $(a \cdot b) \cdot c = a \cdot (b \cdot c) = a \cdot b \cdot c$               |

| Distributivité            | $(a+b)\cdot c = (a\cdot c) + (b\cdot c)$ , $(a\cdot$                                |

|                           | $b) + c = (a+c) \cdot (b+c)$                                                        |

| Théorème d'absorption (1) | $a + (a \cdot b) = a$ , $a \cdot (a + b) = a$                                       |

| Théorème d'absorption (2) | $a \cdot \overline{b} + b = a + b$ , $(a + \overline{b}) \cdot b = a \cdot b$       |

| Théorème d'adjacence      | $(a + \overline{b}) \cdot (a + b) = a$ , $a \cdot \overline{b} + a \cdot b =$       |

|                           | a                                                                                   |

Table 1.3: Théorèmes de Boole

#### 1.4.2 Les théorèmes de De Morgan

Ces deux théorèmes sont plus subtiles :

Théorème 1:

$$\overline{(x+y)} = \overline{x} \cdot \overline{y}$$

Théorème 2:

$$\overline{(x\cdot y)}=\overline{x}+\overline{y}$$

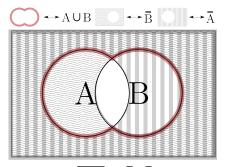

$\overline{A \cup B} = \overline{A} \cap \overline{B}$

$\overline{A \cap B} = \overline{A} \cup \overline{B}$

FIGURE 1.1: Illustration des théorèmes de De Morgan

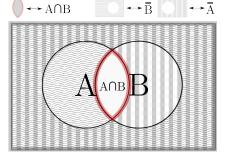

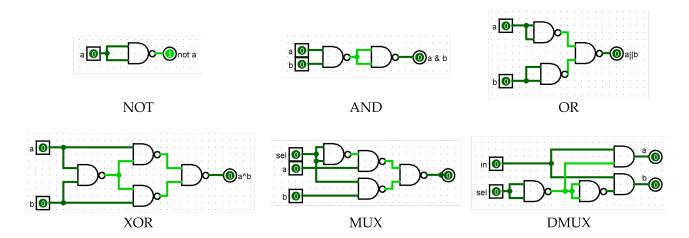

FIGURE 1.2: Ensemble de porte logique fabriquée à partir des règles de construction du jeu Minecraft

On peut noter la symétrie entre les deux théorèmes dans le rôle joué par l'opérateur et (·) et l'opérateur ou (+).

Une illustration du théorème est présentée sur la figure 1.1.

## 1.5 Les portes logiques

Une porte est un dispositif physique qui implémente une fonction booléenne.

Il est important de noter que l'effet physique mise en jeu pour créer la porte logique n'a pas d'importance. Dès qu'une technologie permet de transporter l'information et d'avoir à disposition des interrupteurs, on peut l'utiliser pour créer des portes logiques. On utilise évidemment principalement les flux d'electrons (i.e. le courant electrique), mais on peut très bien aussi utilisé d'autre technologie comme par exemple des circuits optiques, magnétiques, pneumatique, hydrauliques, biologiques, etc (voir figure 1.2)

#### 1.5.1 Porte NON (NOT)

La sortie d'une porte non prend le niveau logique opposé à celui de l'entrée.

Du fait que l'opérateur *non* est unaire, la porte non n'a qu'une entrée (et une sortie).

Le symbole de cette porte ainsi que la table de vérité sont donnés sur la figure 1.3

#### 1.5.2 Porte OU (OR)

La sortie d'une porte OU est dans l'état 1 si au moins une de ses entrées est dans l'état 1.

#### 1.5.3 Porte ET (AND)

La sortie d'une porte ET est dans l'état 1 si et seulement si *toutes* ses entrées sont dans l'état 1

#### 1.5.4 Porte OU-EXCLUSIF (XOR)

La sortie d'une porte XOR est dans l'état 1 si exactement une seule de ses entrées est dans l'état 1.

#### 1.5.5 Porte NON-ET (NAND)

La sortie d'une porte NON-ET (NAND) est au niveau o seulement si les deux entrées sont au niveau 1.

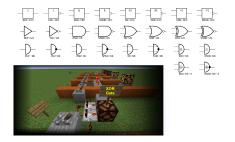

| Nom       | Symbole      | Table de vérité                                                                                                                                                 | Nom  | Symbole     | Table de vérité                                                                                                                                           |

|-----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| OR (ou)   | <b>→</b>     | x         y         S=x+y           0         0         0           0         1         1           1         0         1           1         1         1       | XOR  | <b>⇒</b> D- | x         y         S=x^y           0         0         0           0         1         1           1         0         1           1         1         0 |

| AND (et)  | <del>-</del> | x         y         S=x.y           0         0         0           0         1         0           1         0         0           1         1         1       | NAND | <b>⊅</b> ~  | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                    |

| NOT (non) | <b>*</b>     | x         y         S=x           0         na         1           na         na         na           1         na         0           na         na         na | NOR  | <b>⊅</b> ~  | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                    |

FIGURE 1.3: Liste des principales portes logiques

La porte NAND est particulièrement prisée en recherche fondamentale et elle est parfois qualifiée de graal des portes logiques. En effet, avec uniquement des portes<sup>3</sup> NAND, il est possible de réaliser toutes les autres portes logiques. Ainsi, la plupart des laboratoires en recherche fondamentale portent leur effort sur la mise au point, souvent à base de système nanoscopique, d'une porte NAND.

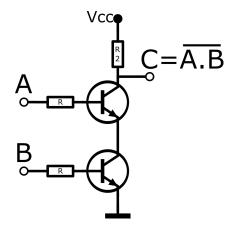

Un exemple d'une réalisation possible de porte NAND à partir de transistor est donnée sur la figure 1.4.

### *1.5.6 Porte NI (NOR)*

La sortie d'une porte NI (NOR) est au niveau 1 seulement si les deux entrées sont au niveau o.

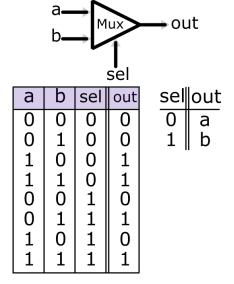

#### *Multiplexeur (MUX)* 1.5.7

Un multiplexeur est une porte logique comportant trois entrées sel, a et b. Une de ces entrées, sel, est appelée le "sélecteur" 4.

L'entrée sel de sélection permet de choisir si la sortie est fixée par la valeur a ou la valeur b.

La table de vérité du multiplexeur est donnée sur la figure 1.5.

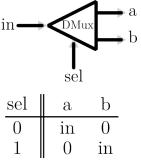

#### Demultiplexeur (DMUX) 1.5.8

Un demultiplexeur est une porte logique possédant deux entrées, in et sel, et deux sorties, a et b. Elle effectue la fonction inverve d'un 3. On peut arriver au même résultats en n'utilisant que des portes NOR

FIGURE 1.4: Schéma d'une porte NAND en utilisant des transistors. La tension en C vaut Vcc (i.e. la valeur booléene 1) sauf si le transistor T1 et le transistor T2 sont passants (c'est à dire A=B=1) car alors C est relié à la masse.

FIGURE 1.5: Schéma d'un multiplexeur, sa table de vérité et sa table de vérité simpli-

4. Un meilleur nom pour cette porte aurait d'ailleurs pu être un "selecteur". Le nom multiplexeur provient des télécommunications où il faut souvent faire passer successivement plusieurs signaux provenant de différentes sources sur un seul cable.

FIGURE 1.6: Schéma d'un demultiplexeur et sa table de vérité simpplifiée.

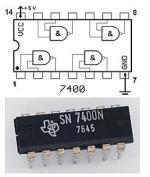

FIGURE 1.7: Image et schéma d'une puce 7400 qui contient 4 portes NAND.

5. Ainsi que des FPGA (Field-Programmable Gate Array)

multiplexeur. L'entrée sel de selection permet d'aiguiller l'entrée vers la sortie a ou la sortie b.

La table de vérité du demultiplexeur est donnée sur la figure 1.6.

## Mise en pratique

Nous traitons ici de l'utilisation pratique en électronique, mais rappelons l'universalité de la logique boolèene. Tout système permettant d'établir est apte à être utiliser pour effecteur de la logique boolèenne.

Sauf cas extrêmement particulier on ne construit pas soi-même les portes logiques à partir de transistor. On peut par exemple directement utilisé des circuits intégré comme par exemple ceux de la famille "74" (cf figure 1.7). On parle de *logique cablé*. Mais cette approche tend à disparaitre pour être remplacé, comme nous le verrons dans la deuxième partie de ce cours, par l'utilisation de micro-controlleur 5. En d'autre terme, la logique câblée est remplacé par la logique programmée.

La logique programmée permet de se passer de nombreux câble qui sont souvent sources d'erreur, peu fiables et surtout très peu flexibles (ou sens de non reprogrammable).

## Quelques exercices autour de l'algébre boléene

## Exercice 1

1. Simplifier l'expression:

$$S = (\overline{A} + B) \cdot (A + B)$$

2. Simplifier l'expression:

$$S = A \cdot C \cdot D + \overline{A} \cdot B \cdot C \cdot D$$

Exercice 2 Simplifiez les expressions suivantes en utilisant les théorèmes de De Morgan:

1.

$$S = \overline{\overline{A} \cdot B \cdot \overline{C}}$$

2.

$$S = \overline{\overline{A} + B \cdot \overline{C}}$$

3.

$$S = \overline{\overline{A} \cdot B \cdot \overline{C \cdot D}}$$

4.

$$S = \overline{A \cdot \overline{(B + \overline{C})}} \cdot D$$

5.

$$S = \overline{(A + \overline{B}) + (B + \overline{A})}$$

6.

$$S = \overline{\overline{\overline{A \cdot B} \cdot CD}}$$

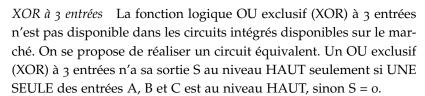

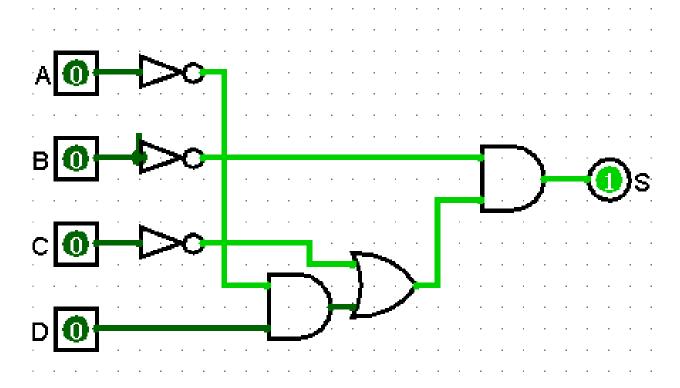

#### Exercice 3

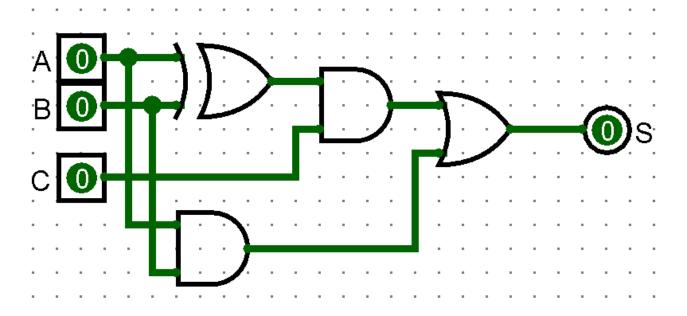

- 1. Donner l'expression booléenne de la sortie S du schéma présenté sur la figure 1.8

- 2. Établir la table de vérité

- 3. Proposez un schéma simplifié.

- 2. Etablir l'expression booléene de S

- 3. Simplifier l'expression précédente

- Réaliser le circuit sous logisim et vérifier son comportement.

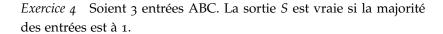

- 1. Donner sa table de vérité

- 2. Donner l'expression logique et tenter de la simplifier

- 3. Donner le schéma lié à cette fonction.

- 4. Réaliser le montage correspondant avec des circuits de la famille 7400.

#### 1.7.2 De l'universalité de la porte NAND

Avec comme seul composant des portes NAND créer un circuit (via logisim ou sur feuille) qui se comporte comme :

- 1. Une porte NON

- 2. Une porte ET

- 3. Une porte OU/XOR

- 4. Un multiplexeur/demultiplexeur.

FIGURE 1.8: Exercice 3

## 2 Arithmétique Booléenne

Après avoir vu l'universalité de la logique booléenne dans le chapitre précédent, nous allons voir maintenant voir comment représenter en binaire des nombres algébriques (via la méthode du complément à 2 ) et fractionnaire (via l'écriture en virgule fixe).

Nous verrons ensuite comment additionner et multiplier deux nombres binaires. Nous implémenterons alors en porte logique un additionneur. Il s'agit d'une opération primordiale d'un ordinateur car d'un certain point de vue la plupart des opérations effectué par un ordinateur peuvent être ramenée à l'addition de nombre binaire.

En suivant la démarche proposée par le livre "The element of computing system" Nisan and Schocken [2008], nous allons construire une Unité arithmétique et logique (ALU) rudimentaire mais relativement puissante.

#### 2.1 Les nombres binaires

Soit  $x = (x_n x_{n-1} \dots x_0)$  une suite de chiffre <sup>1</sup>. La valeur de x en base b, qui s'écrit  $(x)_b$  vaut :

$$(x_n x_{n-1} \dots x_0)_b = \sum_{i=0}^n x_i \cdot b^i$$

ce qui donne par exemple en base 2 :

$$(x_n x_{n-1} \dots x_0)_2 = \sum_{i=0}^n x_i \cdot 2^i$$

(2.1)

Ainsi le nombre (0101)<sub>2</sub> vaut :

$$(0101)_2 = 1 \cdot 2^0 + 0 \cdot 2^1 + 1 \cdot 2^2 + 0 \cdot 2^3 = 5$$

## 2.2 Addition binaire

L'addition binaire suit les même règles que l'addition en base décimale. 1. Un chiffre est un caractère auquel on attribut une valeur entière positive. En base 2 on travaille typiquement avec les caractères 0 et 1, en base 10, 0,1,2,3,4,5,6,7,8, et 9 auquel on ajoute traditionnellement A,B,C,D,E et F en base 16 par exemple.

Figure 2.1: Xkcd - 1 to 10 - https://xkcd.com/953/ - Randall Munroe

| (1) | (1) | (1) |   |   |

|-----|-----|-----|---|---|

|     | O   | 1   | 1 | O |

| +   | 1   | O   | 1 | 1 |

| 1   | 0   | 0   | 0 | 1 |

Table 2.1: Exemple de l'addition de 6 + 11 =

## Nombre binaire algébrique

Nous allons utiliser la méthode qui est de nos jours la plus commune<sup>2</sup>: le complément à 2.

Le complément à 2 est mathématiquement décrit par :

$$\overline{x} = \begin{cases} 2^n - x & \sin x \neq 0 \\ 0 & \sin n \end{cases}$$

(2.2)

Le tableau 2.2 donne un comptage binaire avec 4 bits en prenant en compte le complément à 2.

Nbre positifs Nbre négatif 0000 0 1 0001 1111 -1 2 0010 1110 -2 0011 1101 3 -3 0100 1100 4 -4 5 0101 1011 **-**5 6 0110 1010 7 0111 1001 -7 1000 -8

- On peut coder  $2^n$  nombres allant de  $-2^{n-1}$  à  $2^{n-1} 1$

- Le code des nombres positif commence par un 0

- Le code des nombres négatifs commence par un 1

- On obtient le code de -x à partir de celui de x à partir de la méthode suivante:

- 1. En partant des bits de poids faible (ceux à droites), passer tous les 0 jusqu'à arriver au premier 1.

- 2. Inverser alors tous les bits suivants jusqu'au bit de poids de fort.

On peut aussi, et cela est plus facile à implémenter avec des portes logiques, inverser tous les bits  $^3$  de x et ajouter 1.

Un des grand avantage du complément à 2 et qu'il conserve l'addition binaire sans avoir à faire attention si les nombres sont positifs ou négatifs. Ainsi, d'un point de vue matériel, il n'y a pas à rajouter de porte logique pour prendre en compte les nombres négatifs.

2. Il existe bien d'autre méthode, on pourrait par exemple penser à dédier le bit de poids fort au signe et laisser les autres bits intacts. Ainsi par exemple 0101 serait 5 et 1101 serait -5. Cette méthode est simple à intégrer mais par contre elle ne conserve pas l'opération d'addition binaire alors que cela est le cas pour le complément à 2

TABLE 2.2: Représentation des nombres algébriques binaires à 4 bits en prenant en compte le complément à 2

3. Vous pouvez en effet vérifier avec le tableau 2.2, que lorsque l'on inverse les bits d'un nombre binaire ( $x \leftrightarrow \overline{x}$ , on obtient, dans le cadre du complément à 2 la valeur -x-1. Écrit de façon plus compact :

$$\overline{x} \leftrightarrow -x - 1$$

)

## Représentation d'un nombre en virgule fixe

Il existe principalement 4 deux méthodes pour écrire en binaire des nombres réels:

- La représentation en virgule flottante.

- La représentation en virgule fixe.

codé binaire" (BCD) qui est facile à lire mais qui n'est pas la plus compact en terme d'espace mémoire.

4. Citons aussi la représentation "Décimal

## 2.4.1 La réprésentation en virgule flotante

La réprésentation en virgule flotante est, par exemple, celle qui est utilisée pour stocker un "float" en langage C. Nous n'allons pas spécialement rentrer dans les détails de cette représentation car nous n'allons pas l'utiliser par la suite. Néanmoins, en quelque mots, il s'agit de transcrire en binaire la notation scientifique. On repartie les bits (par exemple les 32 bits pour une variable de type float) de la manière suivante:

- Le premier bits code pour le signe de l'exposant

- Les 8 bits suivant codent pour l'exposant de la puissance de dix

- et les 23 bits restants (mantisse ou significande) code, en binaire complémenté à deux, la partie décimale

Additionner ou multiplier de telle nombres demande, d'une part, de séparer exposant et mantisse et ensuite d'effectuer plusieurs manipulation de ces quantités, et enfin de récoder le nombre obtenue en représentation en virgule flottante. Cela demande beaucoup <sup>5</sup> d'instructions au processeur, même pour une simple addition, si bien qu'il faut souvent une puce (ou une partie de puce) dédiée à la gestion de ces calculs, on parle d'unité de calcul en virgule flottante.

Le processeur que nous allons mettre au point dans la suite de ce cours ne gérera pas la représentation en virgule flottante.

#### 5. Par exemple, pour un micro-contrôleur de type ARM cortex M3, une addition de deux nombres en virgule flottante (float ou double) demande 60 fois de temps de calcul qu'une addition de deux nombres entiers (int)

## La réprésentation en virgule fixe

Comme son nom l'indique, le principe est de fixer un nombre donné de bit après la virgule. Par exemple, pour un nombre codé sur 16bits, on peut considerer que 8 bits (ceux de poids faible), sont alloué à la représentation de la partie décimale.

Ainsi, les 8 bits de poids fort 6 codent pour la partie entière alors que les 8 bits de poids faibles codent pour pour la partie décimale (après la virgule). Soit un nombre *n* codé en binaire sous 16 bits :

$a_1a_2a_3a_4$   $a_5a_6a_7a_8$   $b_1b_2b_3b_4$   $b_5b_6b_7b_8$

alors sa représentation en décimale sera ici 7 :

- 6. Rappelons que l'endroit où on place la virgule est arbitraire. Par contre, evidemment, une fois ce choix fait, il faut s'y tenir.

- 7. Nous utilisons ici, implicitement, un facteur d'échelle (scaling factor) de 2, on peut parfois aussi utiliser un facteur d'échelle de 10.

$$n = a_1 \times 2^7 + a_2 \times 2^6 + a_3 \times 2^5 + a_4 \times 2^4 + a_5 2^3 + a_6 \times 2^2 + a_7 \times 2^1 + a_8 \times 2^0 + b_1 \times 2^{-1} + b_2 \times 2^{-2} + b_3 \times 2^{-3} + b_4 \times 2^{-4} + b_5 2^{-5} + b_6 \times 2^{-6} + b_7 \times 2^{-7} + b_8 \times 2^{-8}$$

(2.3)

Par exemple le nombre :

vaut:

$$2^{3} + 2^{0} + 1 \times 2^{-1} + 0 \times 2^{-2} + 0 \times 2^{-3} + 1 \times 2^{-4} + 2^{-5} + 2^{-6} + 2^{-7} = 9.617$$

Mathématiquement, pour un nombre X de N bits dont chaque bit est noté  $a_i$  et dont  $n_e$  bits codent la partie entière et  $n_f$  la partie fractionnaire, la valeur de nombre X est donnée par :

$$X = \sum_{i=0}^{N-1} a_i 2^{i-n_f} \tag{2.4}$$

Ce qui peut se réécrire :

$$X = 2^{-n_f} \sum_{i=0}^{N-1} a_i 2^i = 2^{-n_f} X_{\text{entier}}$$

(2.5)

où  $X_{\rm entier}$  est la valeur du nombre en base 2 lorsque l'on ne tient pas compte d'une virgule fixe (cf equation 2.1). Il s'agit ainsi d'un moyen rapide d'obtenir rapidement la valeur d'un nombre en virgule fixe ou inversement son écriture. Reprenons l'exemple du nombre :

La valeur  $X_{\rm entier}$  est  $^8$  de 2462. En plaçant comme auparavant la virgule sur le 8ème bit de poids fort, le nombre de bit  $n_f$  codant la partie fractionnaire vaut  $n_f=8$ . La valeur décimale associée, en vertu de l'équation 2.5, est donc :

0000 1001 1001

$$1110 \rightarrow 2^{-n_f} X_{\text{entier}} = 2^{-8} \times 2462 = 9.617875$$

Inversement, si on veut coder le nombre décimale  $\sqrt{2}\approx 1.41421$  avec la représentation en virgule fixe précédente, on divise ce nombre par  $2^{-n_f}$ , en l'occurrence  $2^{-8}$ , et on écrit en binaire la partie entière du nombre obtenu. Cela donne ici :

$$1.41421 \rightarrow 1.41421 \times 2^8 = 362 \rightarrow 0000 \quad 0001 \quad 0110 \quad 1010$$

On peut alors vérifier le résultat, en effet la partie décimale étant les 8 bits de poids faible soit 0110 1010 ce qui donne comme valeur (cf eq 2.3) :

$$2^{-2} + 2^{-3} + 2^{-5} + 2^{-7} = 0.25 + 0.125 + 0.03125 + 0.007812 = 0.414063$$

ce qui est bien la représentation la plus exacte sur 8bits de la partie fractionnaire du nombre  $\sqrt{2}\approx 1.41421$

Vous pouvez trouver en ligne ou sur la calculatrice livrée avec windows en mode "programmeur" des outils pour passer rapidement de la notation binaire (et héxadécimale) à la notation décimale

Avantage et inconvénient de cette représentation Une telle représentation permet de conserver les règles du complément à deux de l'addition binaire. Cependant, elle présente deux principaux écueils :

- Il y a une perte importante de précision sur la partie décimale.

- Il faut faire plus attention au risque de débordement (overflow) de la partie entière. Par exemple, pour le nombre codé en 16 bits dont 8 bits sont dédiés à la partie décimale, il ne reste plus que 8 bits pour la partie entière soit une valeur maximale de 255 on à deux.

## 2.4.3 La multiplication

La multiplication suit les même régles qu'en notation décimale.

|   |   |   |   | O | 1 | 1 | O |

|---|---|---|---|---|---|---|---|

|   |   |   | X | 1 | O | 1 | 1 |

|   |   |   |   | О | 1 | 1 | О |

|   |   |   | O | 1 | 1 | O |   |

|   |   | O | O | O | O |   |   |

|   | O | 1 | 1 | O |   |   |   |

| О | 1 | О | О | О | О | 1 | О |

TABLE 2.3: Exemple de la multiplication de  $6 \times 11 = 66$

La multiplication de deux nombres de *n* bits conduit à un résultat sur 2n bits.

Lorsque le nombre est codé avec une virgule fixe, avec la virgule placée sur le bits  $n_f$ , la virgule après multiplication est déplacée vers la gauche de  $2n_f$  bits. Par exemple si on multiplie 2 nombres codés sur 8 bits dont la virgule est placé sur le 4ème bits, le résultats de la multiplication sera du 16 bits et la virgule sur le bits  $2 \times 4 = 8$ . Autre exemple, si multiplie deux nombres codés sur 16bits, dont la virgule est placée sur le 15ème bits 9, le résultat est sur 32bits avec la virgule placée sur le bit numéro  $2 \times 15 = 30$ .

A noter : une multiplication par 2 correspond à un décalage des bits vers la gauche.

#### 9. Il s'agit d'un choix assez pertinent lorsque l'on sait que les nombres à coder sont inférieur à 1

## 2.4.4 La division par 2

Une division par 2 correspond à un décalage des bits vers la droite.

#### Les additionneurs

On cherche à réaliser l'opération d'addition binaire avec des portes logiques 10.

Nous allons décomposés l'addition en 3 sous opérations :

— Un demi additionneur (half-adder) qui additionne deux bits

10. C'est à dire, i fine, uniquement avec des portes NAND, puisque nous avons vu dans le chapitre précédent que n'importe quelle porte peut être réalisée avec uniquement des portes NAND.

- Un additionneur complet (full-adder) qui additionne trois bits

- L'additionneur qui additionne deux nombres de n bits.

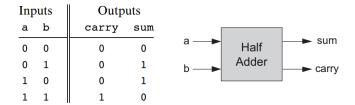

#### 2.5.1 Le demi additionneur

Cette puce, dont le cahier des charges est donné sur la figure 2.2, réalise l'addition binaire des 2 bits d'entrée a et b. La puce possède deux sorties sum (la somme) et carry (retenue en français). Bien qu'il y ait besoin de 4 combinaisons pour lister les couples de valeurs d'entrée a et b, le résultat lui ne peut prendre que trois valeurs : 0, 1 et 2. Le résultat de l'addition est gérer par les deux bits de sortie :

- sum s'occupe des cas 0 et 1

- si les deux bits *a* et *b* sont égaux à 1, le résultat (10) ne peut pas être stocké sur 1 seul bits. On utilise alors le bits de sortie carry pour transmettre ce dépassement.

Dit autrement, le bit de sortie *sum* représente le bit de poids faible de l'addition et le bit de sortie *carry*, le bits de poids fort de l'addition.

```

Chip name: HalfAdder

Inputs: a, b

Outputs: sum, carry

Function: sum = LSB of a + b

carry = MSB of a + b

```

FIGURE 2.2: Cahier des charges du demi additionneur

#### 2.5.2 L'additionneur complet

Cette puce, dont le cahier des charges est donné sur la figure 2.3, réalise l'addition de trois nombres binaires. Ces 3 nombres seront, dans la suite, d'une part deux nombres binaires à additionner et d'autre part la carry d'un autre additionneur complet.

Bien que cela ne soit pas indispensable, nous implémenterons cette puce à partir du demi additionneur.

## 2.5.3 L'additionneur

Le cahier des charges de cette puce est donné sur la figure 2.5.3.

Pour fixer les idées, on va construire un additionneur 8bits. En d'autre termes, deux nombres binaires, *A* et *B*, codés sur 8bits, sont addi-

| a | b | С | carry | sum |            |     |

|---|---|---|-------|-----|------------|-----|

| 0 | 0 | 0 | 0     | 0   |            |     |

| 0 | 0 | 1 | 0     | 1   | a <b>→</b> |     |

| 0 | 1 | 0 | 0     | 1   |            | ſ   |

| 0 | 1 | 1 | 1     | 0   | b —        | . I |

| 1 | 0 | 0 | 0     | 1   | c —        |     |

| 1 | 0 | 1 | 1     | 0   |            |     |

| 1 | 1 | 0 | 1     | 0   |            |     |

| 1 | 1 | 1 | 1     | 1   |            |     |

Chip name: FullAdder Inputs: a, b, c Outputs: sum, carry

Function: sum = LSB of a + b + c carry = MSB of a + b + c

FIGURE 2.3: Cahier des charges de l'additionneur complet

Chip name: Add16

Inputs: a[16], b[16] Outputs: out[16] Function: out = a + b

Comment: Integer 2's complement addition.

Overflow is neither detected nor handled.

11. si A+B>255 sans complément à deux ou A+B<-128 ou A+B>127 avec un complément à deux

tionnés pour donner un nombre binaire C codé sur 8bits lui aussi. Un éventuel dépassement <sup>11</sup> n'est ni détecté, ni géré par la puce.

Nous implémenterons cette puce via l'utilisation en cascade de plusieurs additionneur complets.

### 2.5.4 Incrémenteur

Cette puce est un cas particulier d'additionneur, son cahier des charges est donné sur la figure 2.4.

Chip name: Add16

Inputs: a[16], b[16]

Outputs: out[16]

Function: out = a + b

Comment: Integer 2's complement addition.

Overflow is neither detected nor handled.

FIGURE 2.4: Cahier des charges de l'incrémenteur

## 2.6 L'unité Arithmétique et Logique (ALU)

Toutes les puces que nous avons réalisées jusqu'à maintenant sont génériques et se retrouve dans n'importe qu'elle processeur. L'unité Arithmétique et Logique (ALU), qui va être la puce centrale du processeur est elle spécifique à chaque architecture. Nous suivons ici l'architecture proposé par NISAN et Schocken dans leur livre "The Elements of Computing Systems: Building a Modern Computer from First Principles" Nisan and Schocken [2008]. Cette architecture, a visée pédagogique, a pour but d'offrir le maximum de fonctionnalités avec un nombre minimum de porte logique.

Le cahier des charges de la puce est donnée sur la figure 2.5.

La puce à 8 entrées :

- Deux entrée 16 bits, *x* et *y* sur lesquelles sont réalisés les opérations de l'ALU

- Six entrée de contrôle chacune sur 1 bit. Ces entrées indiquent quelle opération doit être réaliser par l'ALU parmi les 18 prévus 12.

La puce à 3 sorties :

- f(x,y) codé sur 16 qui est le résultat du calcul de l'ALU avec les entrées x et y

- Deux sorties de contrôle chacune sur 1 bit.

12. On peut a priori coder  $2^6 = 64$  fonctions pour l'ALU. L'implémentation prévu dans la référence Nisan and Schocken [2008] se restreint à documenter 18 fonctions réalisant un bon compromis entre polyvalence et simplicité d'implémentation et d'utilisation. Dit autrement, l'ALU, sans aucune autre modification est capable de réaliser d'autre opérations non listés ici.

```

Chip name: ALU

Inputs:

x[16], y[16], // Two 16-bit data inputs

// Zero the x input

zx,

// Negate the x input

nx,

// Zero the y input

zy,

// Negate the y input

ny,

// Function code: 1 for Add, 0 for And

// Negate the out output

no

Outputs:

out[16],

// 16-bit output

// True iff out=0

zr,

// True iff out<0

ng

Function: if zx then x = 0

// 16-bit zero constant

// Bit-wise negation

if nx then x = !x

// 16-bit zero constant

// Bit-wise negation

if zy then y = 0

if ny then y = !y

if f then out = x + y // Integer 2's complement addition

else out = x & y // Bit-wise And

if no then out = !out // Bit-wise negation

if out=0 then zr = 1 else zr = 0 // 16-bit eq. comparison

if out<0 then ng = 1 else ng = 0 // 16-bit neg. comparison

Comment:

Overflow is neither detected nor handled.

```

FIGURE 2.5: Cahier des charges de l'ALU

14. La soustraction x - y est réalisé via l'opération :

$$x - y \leftrightarrow !((!x) + y) \leftrightarrow \overline{\overline{x} + y}$$

En effet, rappelons comme mentionnée dans une note précédente que, dans le cadre du complément à 2 :

$$\overline{x}(=!x) \leftrightarrow -x-1$$

L'opération  $\overline{x} + y$  conduit donc à -x - 1 + y et prendre l'inverse (opérateur!) de ce résul-

La liste des fonctions <sup>13</sup> réalisées par l'ALU est donnée dans la figure 2.6. Parmi ces instruction se trouve l'addition, la soustraction <sup>14</sup>, la négation, le "et" et le "ou" logique, l'incrémentation mais pas la multiplication ou la division. Les opérations manquantes <sup>15</sup> seront implémentés à partir des 18 fonctions de base de l'ALU dans le chapitre 4. En d'autre termes, il n'y pas d'implémentation hardware (i.e physique) de la multiplication mais une implémentation software (via la programmation d'une séquence d'opérations).

|    | These bits instruct<br>how to preset<br>the x input |                       | These bits instruct<br>how to preset<br>the y input |                       | This bit selects<br>between<br>+ / And | This bit inst.<br>how to<br>postset out | Resulting<br>ALU<br>output |

|----|-----------------------------------------------------|-----------------------|-----------------------------------------------------|-----------------------|----------------------------------------|-----------------------------------------|----------------------------|

|    | zx                                                  | nx                    | zy                                                  | ny                    | f                                      | no                                      | out=                       |

| 15 | if zx<br>then<br>x=0                                | if nx<br>then<br>x=!x | if zy<br>then<br>y=0                                | if ny<br>then<br>y=!y | if f then out=x+y else out=x&y         | if no<br>then<br>out=!out               | f(x,y)=                    |

|    | 1                                                   | 0                     | 1                                                   | 0                     | 1                                      | 0                                       | 0                          |

|    | 1                                                   | 1                     | 1                                                   | 1                     | 1                                      | 1                                       | 1                          |

|    | 1                                                   | 1                     | 1                                                   | 0                     | 1                                      | 0                                       | -1                         |

|    | 0                                                   | 0                     | 1                                                   | 1                     | 0                                      | 0                                       | x                          |

|    | 1                                                   | 1                     | 0                                                   | 0                     | 0                                      | 0                                       | У                          |

|    | 0                                                   | 0                     | 1                                                   | 1                     | 0                                      | 1                                       | !x                         |

|    | 1                                                   | 1                     | 0                                                   | 0                     | 0                                      | 1                                       | !y                         |

|    | 0                                                   | 0                     | 1                                                   | 1                     | 1                                      | 1                                       | -x                         |

|    | 1                                                   | 1                     | 0                                                   | 0                     | 1                                      | 1                                       | -у                         |

|    | 0                                                   | 1                     | 1                                                   | 1                     | 1                                      | 1                                       | x+1                        |

|    | 1                                                   | 1                     | 0                                                   | 1                     | 1                                      | 1                                       | y+1                        |

|    | 0                                                   | 0                     | 1                                                   | 1                     | 1                                      | 0                                       | x-1                        |

|    | 1                                                   | 1                     | 0                                                   | 0                     | 1                                      | 0                                       | y-1                        |

|    | 0                                                   | 0                     | 0                                                   | 0                     | 1                                      | 0                                       | x+y                        |

|    | 0                                                   | 1                     | 0                                                   | 0                     | 1                                      | 1                                       | x-y                        |

|    | 0                                                   | 0                     | 0                                                   | 1                     | 1                                      | 1                                       | y-x                        |

|    | 0                                                   | 0                     | 0                                                   | 0                     | 0                                      | 0                                       | x&y                        |

|    | 0                                                   | 1                     | 0                                                   | 1                     | 0                                      | 1                                       | х у                        |

FIGURE 2.6: Table de vérité l'ALU

## 2.7 TD 2

## 2.7.1 Complément à 2

- 1. Quelle est la valeur maximale et la valeur minimale que l'on peut atteindre avec 5 chiffres binaires tout en prenant en compte le complément à 2.

- 2. Dresser le tableau de correspondance de ces 32 nombres binaires avec leur équivalent en base décimale

- 3. Vérifier que:

- (a) 8 + (-11) = -3

- (b) -5 + (13) = 8

Représentation d'un nombre en virgule fixe

- 1. Donner la plus exacte approximation du nombre  $\pi$  sur 8 bits.

- 2. Effecteur, sur 8 bits et sans complément à deux, le calcul 8.31 + 2.42.

## 2.7.2 Additionneur

En suivant les indications données dans les sections 2.5.1, 2.5.2, 2.5.3 et 2.5.4, construire avec logisim les puces réalisant : le demi-additionneur, l'additionneur complet, l'additionneur 8 bits et l'incrémenteur.

## 2.7.3 ALU

En suivant les indications données dans les sections 2.6 construire avec logisim l'ALU que nous allons utilisé par la suite.

NB: La transcription d'un "if" (si logique) est, en terme de porte logique un multiplexeur.

## 3 Logique séquentielle

Dans ce chapitre, nous cherchons à construire avec des portes logiques des circuits capables de conserver en mémoire des variables booléennes.

Les circuits vus dans les deux derniers chapitres présentent des sorties qui ne dépendent pas de la valeur des entrées. Le "passé", c'està-dire l'état antérieur n'est pas pris en compte. Il est donc impossible d'envisager la fonction mémoire.

Les circuits logiques séquentiels, à l'inverse des circuits combinatoires, sont des circuits dont la réaction ou l'état dépend des entrées mais aussi des événements précédemment apparus dans le temps.

## 3.1 Quelques généralités

Le fait de retenir une information (en l'occurrence ici un état "0" ou un état "1") est intrinsèquement lié à la notion de *temps*. Il faut pouvoir définir un *maintenant* où on veut avoir retenu l'information qui était présente *avant*.

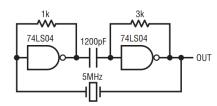

#### 3.1.1 Horloge

Dans la plupart des ordinateurs le passage du temps est matérialisé par une horloge qui délivre a intervalle régulier des impulsions électriques. Ces horloges sont souvent construite autour de quartz <sup>1</sup> taillé de telle sorte qu'il vibre à une fréquence bien définie <sup>2</sup>. Une fois inséré dans un circuit électrique (par exemple celui de la figure 3.2), l'ensemble délivre des impulsions électriques Ces impulsion sont envoyés à tous sous-circuits du processeur qui ont besoin d'une référence temporelle (typiquement les mémoires).

Entre les impulsions de l'horloge l'état de l'ordinateur est indéfini. Plus précisément, les électrons sont encore en mouvement au sein de toutes les portes logiques inter-connectées. Durant ce laps de temps, l'ALU que nous avons mis au point au chapitre précedent donne n'importe quoi comme résultat.

La fréquence maximale que peut prend l'horloge doit donc être telle que l'intervalle entre deux tics laisse le temps, d'une part au signal d'horloge d'arriver aux différentes portes<sup>3</sup> et d'autre part aux élec-

- 1. Le quartz est un milieu piezzo-electrique. D'un point de vue cristallographique le barycentre des charges + et des charges d'une maille elementaire peuvent ne pas coïncider. Ainsi, lorsque l'on compresse un tel cristal, une tension apparait à ses bornes. A contrario, lorsqu'on le soumet à une impulsion electrique, le cristal piezzo-electrique se compresse puis se met à osciller apprès la fin de l'oscillation. Plus exactement, suite à cette excitation impulsionelle, il vibre à à sa pulsation de résonance avec un excellent facteur de qualité Q (typiquement  $Q \approx 100\,000$ )

- 2. Vous pouvez voir par exemple sur un arduino un cristal (qui prend l'aspect d'un boitier métallique oblong) où il est inscrit "T16.000" pour indiquer sa fréquence de vibration à 16 MHz

FIGURE 3.1: Photo d'un boitier contenant un quartz taillé de telle sorte à vibrer à une fréquence extremement précise.

FIGURE 3.2: Exemple d'un circuit rudimentaire mettant en jeu un oscillateur à quartz et des portes logiques pour produire un signal d'horloge

3. Étonnamment, c'est ce point qui limite la montée en fréquence des processeurs (mais pas pour autant en en puissance de calculs) depuis ces quinze dernière année. En effet, les liaisons métalliques au sein du processeur ont nécessairement une resistance et un effet capacitif entre elles ce qui créé un temps de retard  $\tau=RC$ . L'utilisation de photon à la place d'electron (un processeur optique) permettrait de ne plus avoir ce temps de retard et d'augmenter considérablement la fréquence des processeurs (et aussi diminuer leur consommation). Il s'agit d'un projet de recherche toujours actuel mais encore au stage du laboratoire.

trons au sein des portes d'atteindre leur position d'équilibre.

En 2021, la fréquence maximale des processeurs grand public est de l'ordre de 5 GHz. Donc, tous les 200 ps, les électrons s'agitent au sein des portes, trouvent leur position d'équilibre, puis on collecte les résultats données par les circuits (comme l'ALU par exemple) et on repart pour un autre cycle d'horloge ... et tout cela 5 milliards de fois par seconde!

#### 3.1.2 Bascules

Les *bascules* (ou *flip-flop* en anglais) sont les briques de bases des composants liés à la mémoire. Leur mission première est de pouvoir donner à un temps t en signal de sortie, la valeur qui était en entrée à temps  $t_0 < t$ . Dit autrement, son rôle consiste à enregistrer une information non permanente puis à conserver cet état lorsque l'information disparaît. Nous allons voir par la suite leur fonctionnement et comment les implémenter avec des portes logiques.

Ces bascules peuvent être synchrones ou asynchrones. Une bascule asynchrone n'est reliée à aucun système capable de mesurer le défilement du temps. Ces bascules peuvent donc changer d'état à tout moment. A contrario, une bascule synchrone est reliée au signal d'horloge. La bascule ne peut changer d'état que lors de l'arrivée d'une impulsion d'horloge. Ce dernier est alors utilisé pour synchroniser l'ensemble des bascules reliés à l'horloge. Concrètement, une bascule synchrone possédera une entrée pour recevoir le signal de l'horloge là où cela ne sera pas le cas pour une bascule asynchrone.

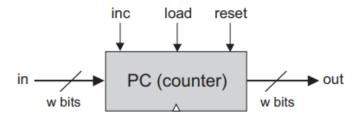

#### 3.1.3 Compteurs

Un compteur est une puce séquentielle qui garde en mémoire un entier et qui s'incrémente à chaque nouveau pulse d'horloge. Ces puces jouent un rôle important dans l'architecture d'un ordinateur <sup>4</sup> par exemple pour savoir quelle instruction executer au tick d'horloge suivant.

## 3.2 Implémentation Bascules à partir de portes logiques

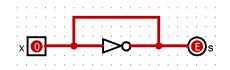

### 3.2.1 Boucler des portes logiques

La bascule doit réaliser la fonction  $out(t) = in(t_0)$  avec  $t > t_0$ . Elle doit donc, d'une façon où d'une autre relié le signal à son entrée au signal en sortie. On parle alors de *boucle* (ou feedback en anglais).

On pourrait alors naïvement essayer de boucler la sortie d'une porte logique vers son entrée. Cela conduit à un état indéfini du système (voir figure 3.3).

FIGURE 3.3: Bouclage d'une porte NOT. La sortie ne sait pas si elle doit prendre la valeur en sortie de porte,  $\bar{x}$ , où la valeur en entrée x.)

<sup>4.</sup> Mais aussi d'un microprocesseur. Un arduino uno possede 3 compteurs aussi appelés timer.)

Il faut utiliser au moins deux portes pour mettre en place le bouclage des portes logiques permettant de conserver un état logique.

## 3.2.2 Bascule RS

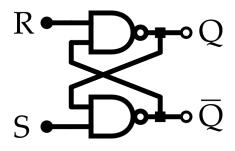

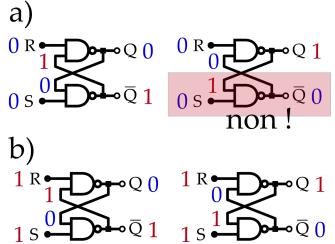

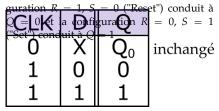

La bascule RS (pour Reset and Set) est présentée sur la figure 3.4. Il s'agit d'une bascule asynchrone car elle fait pas intervenir de signal d'horloge. Étudions son fonctionnement.

La bascule utilise deux portes NAND<sup>5</sup> présentant un bouclage : une des deux entrées d'une porte NAND et relié à la sortie de l'autre porte NAND. Elle possede deux entrée R (Reset) et S (Set) et deux sorties Q et  $\overline{Q}$ . Les signaux Q et  $\overline{Q}$  de sortie dépendent des deux entrée R et S mais aussi de l'état antérieur de Q.

La table de vérité de la bascule est donnée sur la figure 3.5.

On distingue quatre cas de figure :

- Il existe pour la sortie Q un état "interdit" qui est obtenu lorsque R = S = 0. En effet, comme cela est montré sur la figure 3.4, la sortie  $\overline{Q}$  de la bascule n'est pas égale à la valeur opposée de Q.

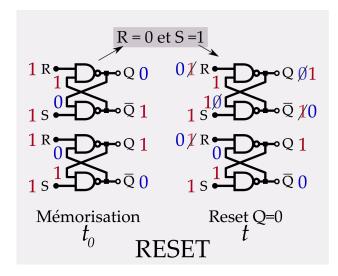

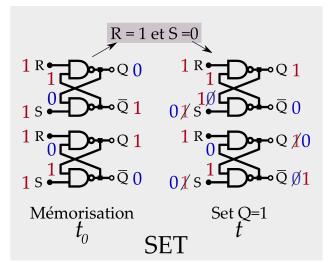

- L'état de "mémorisation" est obtenu pour R = S = 1. La sortie reste égale à la valeur Q qui était déjà en mémoire.

- La mise à zéro ("reset") de la sortie Q (et donc  $\overline{Q} = 1$ ) pour R = 1et S = 0

- La mise à 1 ("set") de la sortie Q pour R = 0 et S = 1.

FIGURE 3.4: Bascule RS implémentée avec des portes NAND

| R | S | Q |              |

|---|---|---|--------------|

| 0 | 0 | X | interdit     |

| 0 | 1 | 1 | mise à 1     |

| 1 | 0 | 0 | mise à 0     |

| 1 | 1 | Q | mémorisation |

Figure 3.5: Table de vérité de la Bascule RS

5. On peut aussi l'implémenter avec deux portes NOR

Nous n'utiliserons pas par la suite la bascule RS car, du fait qu'elle soit asynchrone, il n'est pas possible de faire fonctionner en parallèle et de façon synchronisées plusieurs de ces bascules <sup>6</sup>. Elle constitue néanmoins la brique de base de la bascule D qui est, elle, très utilisée pour les montage synchrone.

FIGURE 3.6: a) État interdit de la bascule RS. La porte NAND indiquée en rouge ne satisfait pas sa table de véritée. b) Mise en mémoire (R = S = 1) pour la bascule RS. Les 6.444 rasdie, fig was larlordes eveleura ar écée dentere drelapsortici il seso Etistables servir parfois à filtrer les rebonds d'interrupteur mécanique.

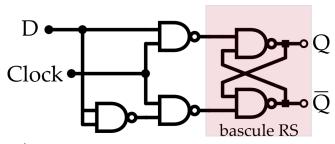

## 3.2.3 Bascule D

FIGURE 3.7: Etat "ReSet" et "Set" de la bascule RS. Quelque soit l'état précedent de la bascule (dans l'état de mémorisation), la confi-

Figure 3.8: Table de vérité de la Bascule D

La bascule *D* est synchrone, son implémentation en porte NAND est donnée sur la figure 3.9 et sa table de vérité sur la figure 3.8.

Il s'agit en fait d'une bascule RS avec un amont un système permettant de synchroniser l'entrée D (comme "Data") avec le signal d'horloge :

- Lorsque D vaut 1 cela revient à faire "set" (S = 0 et R = 1) sur la bascule RS qui garde donc en mémoire 1.

- Lorsque D vaut o cela revient à faire "reset" (R = 0 et S = 1) sur la bascule RS qui garde donc en mémoire 1.

Il s'agit de la brique de base des mémoires que l'on va utiliser par la suite.

FIGURE 3.9: Bascule D implémentée avec des portes NAND. On peut identifier une bascule RS précédé d'un circuit permettant de synchroniser l'entrée D (comme "Data") avec le signal d'horloge (clock). Cette bascule mémorise la valeur de D lorsque l'horloge (clock) vaut 1 (il n'y pas ici de prise en compte de front montant ou descendant).

## 3.3 Implémentation de la mémoire à partir de bascule

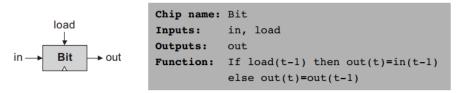

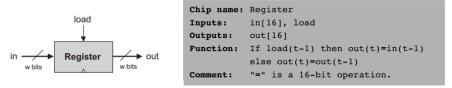

#### 3.3.1 Registre

Le cahier de charge d'un registre est donné sur la figure 3.10. Le registre a pour but de stocker un seul bit d'information (un seul "o" ou "1"). Il possède une entrée et une sortie qui contienne des données codées sur 1bit. La sortie "out" émet l'état actuel du registre. Une

entrée de contrôle "load" indique si on doit écrire dans la mémoire l'état de l'entrée "in".

FIGURE 3.10: Cahier des charges d'un registre

FIGURE 3.11: Cahier des charges d'un registre 16 bits

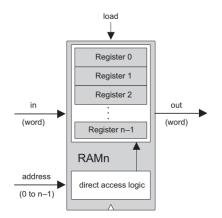

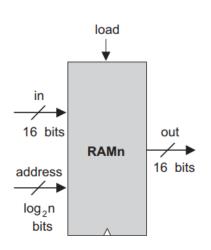

## 3.3.2 Random Access Memory

Une mémoire à accès aléatoire (RAM pour Random Access Memory) est une banque de régistre munie d'un circuit d'aiguillage permettant d'accéder à un de ces registres pour ou lire ou écrire des données. Chaque registre possède un adresse unique. Muni de cette adresse le circuit d'aiguillage (d'adressage) permet de s'adresser au registre souhaité (que ce soit pour écrire une donnée dedans et/ou lire son contenu). Comme on peut le voir sur le cahier des charges (fig 3.13), la RAM possède deux entrées 16 bits, une première pour l'adresse permettant donc de choisir le registre et la deuxième entrée 16 bits pour donner une éventuelle valeur à insérer dans le registre indiqué par l'adresse. En sortie, on obtient la valeur présente dans le registre indiqué par l'adresse.

Compteur

Le cahier des charges d'un compteur est donné sur la figure 3.14.

## 3.4 TD 3

3.3.3

## 3.4.1 bascule D

Reproduire via logisim le schéma de la Bascule D (fig 3.9) et vérifier qu'il correspond bien à sa table de vérité.

## 3.4.2 Registre

En suivant son cahier des charges (fig 3.10) réalisé un registre un bit. Par soucis de performance, on utilisera la bascule D de logisim

7. Dans une telle mémoire, contrairement à un disque dur ou un disque optique, le temps d'accès à un element de mémoire est le même pour tous les elements.

FIGURE 3.12: Schéma du fonctionnement de la Random Access Memomry (RAM)

Chip name: RAMn // n and k are listed below

Inputs: in[16], address[k], load

Outputs: out[16]

Function: out(t)=RAM[address(t)](t)

If load(t-1) then

RAM[address(t-1)](t)=in(t-1)

Comment: "=" is a 16-bit operation.

## The specific RAM chips needed for the Hack platform are:

| Chip name | n     | k  |

|-----------|-------|----|

| RAM8      | 8     | 3  |

| RAM64     | 64    | 6  |

| RAM512    | 512   | 9  |

| RAM4K     | 4096  | 12 |

| RAM16K    | 16384 | 14 |

FIGURE 3.13: Cahier des charges de la Random Access Memomry (RAM)

Chip name: PC // 16-bit counter in[16], inc, load, reset Inputs:

Outputs: out[16]

Function: If reset(t-1) then out(t)=0

else if load(t-1) then out(t)=in(t-1)

else if inc(t-1) then out(t)=out(t-1)+1

else out(t)=out(t-1)

Comment: "=" is 16-bit assignment.

"+" is 16-bit arithmetic addition.

FIGURE 3.14: Cahier des charges du compteur

plutôt que le montage réalisé précédemment.

On rappelle que pour réaliser un aiguillage entre deux parties d'un circuit en fonction d'une troisième variable (l'équivalent d'un "if" en code), on utilise un multiplexeur.

## 3.4.3 RAM

En suivant son cahier des charges (fig 3.13) réaliser, à partir d'une collection de registre et d'un circuit d'aiguillage gérant l'adresse, une mémoire RAM.

Pour minimiser le nombre de connexion à établit tout en gardant la logique de la puce, on réalisera une RAM contenant des données codées sous 4bits et avec un adressage des registres sous 2 bits.

## 3.4.4 Compteur

En suivant son cahier des charges (fig 3.14) réaliser un compteur.

### 4 Langage machine

A partir de porte NAND, nous avons réalisés dans le chapitre 2 une unité d'arithmétique logique (ALU) capable, entre autre de faire des additions et dans le chapitre 3 des mémoires composées d'ensemble de registre adressable (RAM).

Nous allons dans ce chapitre, toujours en suivant la démarche donnée par le livre Nisan and Schocken [2008] assembler ces deux éléments pour créer un processeur. Nous allons tout d'abord parler de l'architecture de l'ordinateur, c'est à dire comment agencer mémoire et ALU. Nous verrons ensuite comment coder les instructions que pourra effectuer le processeur ce qui nous conduira à la notion de langage machine.

Enfin, dans une troisième partie, nous verrons comment programmer cet ordinateur, c'est à dire écrire du code en langage machine afin, par exemple, de calculer une addition, une multiplication ou encore une factorielle.

### 4.1 Architecture de l'ordinateur

Fléxibilité d'un ordinateur via le changement de programme.

Le code du programme est stockée et manipulée dans la mémoire de l'ordinateur exactement comme les données transitant au sein de l'ordinateur.

Harvard vs Von Neuman.

### 4.1.1 Mémoire

Mémoire pour les données High-level programs manipulate abstract artifacts like variables, arrays, and objects. When translated into machine language, these data abstractions become series of binary numbers, stored in the computer's data memory. Once an individual word has been selected from the data memory by specifying its address, it can be either read or written to. In the former case, we retrieve the word's value. In the latter case, we store a new value into the selected location, erasing the old value

Mémoire pour les instructions When translated into machine language, each high-level command becomes a series of binary words, representing machine language instructions. These instructions are stored in the computer's instruction memory. In each step of the computer's operation, the CPU fetches (i.e., reads) a word from the instruction memory, decodes it, executes the specified instruction, and figures out which instruction to execute next. Thus, changing the contents of the instruction memory has the effect of completely changing the computer's operation. The instructions that reside in the instruction memory are written in an agreedupon formalism called machine language. In some computers, the specification of each operation and the codes representing its operands are represented in a singleword instruction. Other computers split this specification over several words

### 4.1.2 Central Processing Unit (CPU)

ALU Il s'agit de l'ALU construite au chapitre 2.

Registre When translated into machine language, each high-level command becomes a series of binary words, representing machine language instructions. These instructions are stored in the computer's instruction memory. In each step of the computer's operation, the CPU fetches (i.e., reads) a word from the instruction memory, decodes it, executes the specified instruction, and figures out which instruction to execute next. Thus, changing the contents of the instruction memory has the effect of completely changing the computer's operation. The instructions that reside in the instruction memory are written in an agreedupon formalism called machine language. In some computers, the specification of each operation and the codes representing its operands are represented in a singleword instruction. Other computers split this specification over several words

### Uniquement deux registres:

Le régistre de données (data register)

Le régistre d'adresses (addressing register)

Le régistre d'instruction (Program counter register)

l'équivalent de notre mémoire à court-terme.

The CPU has to continuously access the memory in order to read data and write data. In every one of these operations, we must specify which individual memory word has to be accessed, namely, supply an address. In some cases this address appears as part of the current instruction, while in others it depends on the execution of a previous instruction. In the latter case, the address should be stored in a register whose contents can be later treated as a memory address—an addressing register.

These registers give the CPU short-term memory services. For example, when calculating the value of (a - b)c, we must first compute and re-

member the value of (a - b). Although this result can be temporarily stored in some memory location, a better solution is to store it locally inside the CPU—in a data register.

*Unité de contrôle* voir section suivante

A computer instruction is represented as a binary code, typically 16, 32, or 64 bits wide. Before such an instruction can be executed, it must be decoded,

and the information embedded in it must be used to signal various hardware devices (ALU, registers, memory) how to execute the instruction. The instruction decoding is done by some control unit, which is also responsible for figuring out which instruction to fetch and execute next. The CPU operation can now be described as a repeated loop: fetch an instruction (word) from memory; decode it; execute it, fetch the next instruction, and so on. The instruction execution may involve one or more of the following micro tasks: have the ALU compute some value, manipulate internal registers, read a word from the memory, and write a word to the memory. In the process of executing these tasks, the CPU also figures out which instruction to fetch and execute next.

### 4.1.3 Notre architecture

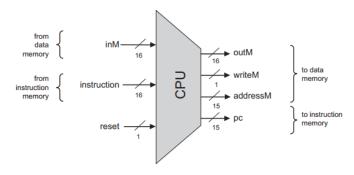

The Hack platform is a 16-bit von Neumann machine, consisting of a CPU, two separate memory modules serving as instruction memory and data memory

he Hack CPU consists of the ALU specified in chapter 2 and three registers called data register (D), address register (A), and program counter (PC). D and A are general-purpose 16-bit registers

While the D-register is used solely to store data values, the contents of the A-register can be interpreted in three different ways, depending on the instruction's context: as a data value, as a RAM address, or as a ROM address

CPU The CPU of the Hack platform is designed to execute 16-bit instructions according to the Hack machine language. It expects to be connected to two separate memory modules: an instruction memory, from which it fetches instructions for execution, and a data memory, from which it can read, and into which it can write, data values. Figure 5.2 gives the specification details

Instruction Memory The Hack instruction memory is implemented in a direct-access Read-Only Memory device, also called ROM. The Hack ROM consists of 32K addressable 16-bit registers, as shown in figure 5.3.

```

Chip Name: CPU

// Central Processing Unit

Inputs:

inM[16],

// M value input (M = contents of RAM[A])

// Instruction for execution

instruction[16],

// Signals whether to restart the current

// program (reset=1) or continue executing

// the current program (reset=0)

// M value output

Outputs:

outM[16],

writeM,

// Write to M?

addressM[15],

// Address of M in data memory

// Address of next instruction

pc[15]

Executes the instruction according to the Hack machine language

specification. The D and A in the language specification refer to

CPU-resident registers, while M refers to the memory location

addressed by A (inM holds the value of this location).

If the instruction needs to write a value to {\tt M}, the value is

placed in outM, the address is placed in addressM, and the writeM

bit is asserted. (When writeM=0, any value may appear in outM.)

If reset=1, then the CPU jumps to address 0 (i.e., sets pc=0 in

the next time unit) rather than to the address resulting from

executing the current instruction.

```

Data Memory Hack's data memory chip has the interface of a typical RAM device, like that built in chapter 3 (see, e.g., figure 3.3). To read the contents of register n, we put n in the memory's address input and probe the memory's out output. This is a combinational operation, independent of the clock. To write a value v into register n, we put v in the in input, n in the address input, and assert the memory's load bit. This is a sequential operation, and so register n will commit to the new value v in the next clock cycle. In addition to serving as the computer's general-purpose data store, the data memory also interfaces between the CPU and the computer's input/output devices, using memory maps.

### 4.2 Langage machine

Arbitraire (mais efficace).

A machine language is an agreed-upon formalism, designed to code low-level programs as series of machine instructions.

A machine language program is a series of coded instructions. For example, a typical instruction in a 16-bit computer may be 1010001100011001. In order to figure out what this instruction means, we have to know the rules of the game, namely, the instruction set of the underlying hardware platform.

x86 1000 instructions différentes (en 2016)

Langage machine, Assembleur, langage haut niveau comme le C et le rôle du compilateur.

Although most people will never write programs directly in machine language, the study of low-level programming is a prerequisite to a complete understanding of computer architectures.

De plus, il est assez fascinant de se rendre compte à quel point les logiciels les plus sophistiqués ne sont, en fait, qu'une longue succession d'instruction extrêmement élémentaires, chacune déclenchant une opération très simple (comme une addition) réalisée à partir de'un agencement de portes logiques.

#### Notre ordinateur 4.2.1

The Hack machine language is based on two 16-bit command types:

- Une instruction de type "adresse" ou "A-instruction"

- Une instruction du type "calcul" ou "C-instruction"

Although the Hack syntax is more accessible than that of most machine languages, it may still look obscure to readers who are not familiar with low-level programming. In particular, note that every operation involving a memory location requires two Hack commands: One for selecting the address on which we want to operate, and one for specifying the desired operation.

### 4.2.2 Instruction adresse

Une isntruction de type A est utilisé pour mettre une valeur codée sur 15-bit dans le régistre d'adresse A du CPU. Elle se code ainsi :

La valeur 0vvv vvvv vvvv codé en binaire est alors mise dans le registre A. Notons que le bit de poids fort de l'instruction est un 0, ce qui permet de la distinguer d'une instruction de type C (voir section 4.2.3) dont le bit de poids fort est un 1.

Par exemple l'instruction:

qui commence par zéro, est donc une instruction de type A et va mettre dans le registre A la valeur 14 (i.e 1110 en binaire).

### 4.2.3 Instruction calcul

Cette instruction est plus complexe que l'instruction A vu precedemment, c'est elle qui déclenche un calcul au sein de l'ALU.

Une instruction de type C à la forme :

111

$$\underbrace{a \quad c_1c_2c_3c_4 \quad c_5c_6}_{\text{calcul}} \underbrace{d_1d_2 \quad d_3}_{\text{dest}} \underbrace{j_1j_2j_3}_{\text{jump}}$$

(4.2)

En partant du bits de poids fort :

- Le premier bit d'identification

- Les deux bits suivants qui ne sont pas utilisés

- La partie calcul contenant 7 bits (a  $c_1c_2c_3c_4$   $c_5c_6$ ) permettant de coder le calcul à effecteur

- La partie destination contenant 3 bits pour coder où stocker le résultat du calcul de l'ALU

Partie Identification L'instruction de type C commence par un 1, ce qui la distingue d'une instruction de type A

Partie calcul La partie calcul (a  $c_1c_2c_3c_4$   $c_5c_6$ ) composés de 7 bits (soit 128 possibilités) permet d'effectuer des calculs à partir de trois sources de données :

- La valeur D contenue dans le registre D

- La valeur *A* contenue dans le registre A

- La valeur M[A] contenue dans la mémoire pointée par l'adresse contenue dans A.

| (when a=0) comp mnemonic | c1 | c2 | <b>c</b> 3 | c4 | <b>c</b> 5 | <b>c</b> 6 | (when a=1)  comp mnemonic |

|--------------------------|----|----|------------|----|------------|------------|---------------------------|

| 0                        | 1  | 0  | 1          | 0  | 1          | 0          |                           |

| 1                        | 1  | 1  | 1          | 1  | 1          | 1          |                           |

| -1                       | 1  | 1  | 1          | 0  | 1          | 0          |                           |

| D                        | О  | 0  | 1          | 1  | 0          | 0          |                           |

| A                        | 1  | 1  | 0          | 0  | 0          | 0          | М                         |

| !D                       | 0  | 0  | 1          | 1  | 0          | 1          |                           |